# LDO レギュレータの特性改善\*

小 浜 輝 彦\*\* 古 賀 健 史\*\*\*

## Stability Improvement of LDO Regulator

Teruhiko KOHAMA\*\* and Kenji KOGA\*\*\*

Low Dropout (LDO) regulator has an advantage of lower dropout voltage compared with other linear regulators. However, LDO requires careful design to ensure stable operation due to inherent instability of the circuit. This paper describes principle of LDO regulator and provides design guidelines for derivative and ESR compensation method. Effects of circuit parameters on the stability of LDO are revealed by circuit simulation and experiments.

Key Words: LDO regulator, Stability, Bode plot, Ceramic capacitor

## 1. まえがき

LDO レギュレータはリニアレギュレータの一種でトランジスタの能動領域を利用して定電圧化を図る電源ICである. LDO 以外のリニアレギュレータには NPN レギュレータ, 準 LDO レギュレータがある. LDO は他のリニアレギュレータに比べて入出力電圧差が小さいため低電圧でも駆動できる特徴を有するが、安定性の面で問題点も残されている. 現在のリニアレギュレータには、電圧降下の低減が一層求められていることから、LDO が使用される機会は増えている. そこで、本稿では LDO の安定性について詳細に解析し、安定性を改善する補償方法についてその設計手順を示す. また、今後主流となるセラミックコンデンサを用いる場合の選定方法についても述べる.

## 2. 動作原理

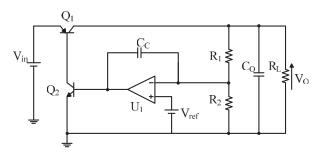

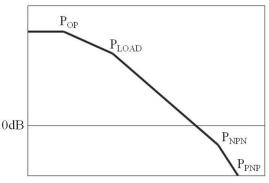

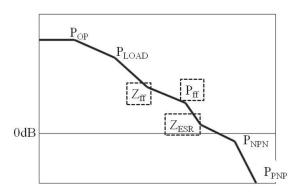

LDO の基本回路を図1に示す. パワートランジスタQ1 がエミッタ接地で用いられており, ドロップアウト電圧は低いが安定性が悪い. この不安定要因は図2に示す制御系の極の数とその位置にある. 低周波にはオペア

図1 LDO 等価回路

図2 極の位置の概略図

ンプによる極  $P_{OP}$  とエミッタ接地により生じる極で負荷の値に影響を受ける  $P_{LOAD}$  があり、さらに高周波領域にはトランジスタによる極  $P_{NPN}$ ,  $P_{PNP}$  が生じている. エミッタ接地を用いるとトランジスタの出力インピーダンスが

<sup>\*</sup> 平成 24 年 5 月 31 日受付

<sup>\*\*</sup> 電気工学科

<sup>\*\*\*</sup> 工学研究科電気工学専攻

图3 [DO 小信与寺间回路

大きな値となる.そのため負荷  $R_L$  の極  $P_{LOAD}$  が低周波に発生する.

このため位相遅れが増大し、帰還が正帰還となり発振現象を引き起こす。一方 NPN レギュレータや準 LDO レギュレータでは  $Q_1$  にあたるパワートランジスタがコレクタ接地であるため、出力インピーダンスが小さな値となる。このため高周波に負荷の極が発生するため安定するが、 $Q_1$  に複数のトランジスタをダーリントン接続しているため電圧降下が大きい。電圧降下の値は LDO が 0.7V 程度であるのに対し、準 LDO レギュレータは 1.4V、NPN レギュレータは 2.1V となっている。

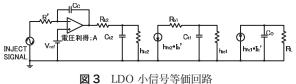

LDO の安定性を考察するには図1の回路について一巡伝達関数を導出し、これから得られる極と零点を調べる必要がある。まず、図1から得られたLDO の小信号等価回路を図3に示す。これから一巡伝達関数を求めると極が式(1)~(4)で表される。

$$P_{OP} = \frac{1}{2\pi AR'C_C} \tag{1}$$

$$P_{LOAD} = \frac{1}{2\pi R_L \cdot C_O} \tag{2}$$

$$P_{NPN} = \frac{1}{2\pi \frac{h_{ie2}R_{b}'}{h_{ie2}+R_{b}}C_{t2}}$$

(3)

$$P_{PNP} = \frac{1}{2\pi h_{ie1} \cdot C_{t1}} \tag{4}$$

## 3. 位相補償

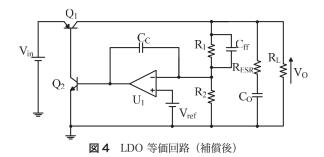

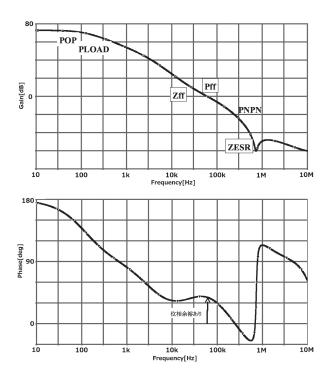

このままの回路では不安定となるため、零点を加える補償によって安定性を図る.補償を加えた回路とそのゲイン特性の概形をそれぞれ図 4、図 5 に示す.まず  $C_{\rm fr}$  による微分補償により図 5 の零点  $Z_{\rm fr}$  を作るが、同時に極  $P_{\rm fr}$  を生じることに注意が必要である.また IC 内部であるため  $C_{\rm fr}$  に容量の制約があり、十分な零点の設置が難しい.そこで出力コンデンサ  $C_{\rm o}$  の等価直列抵抗 ESR で生じる零点  $Z_{ESR}$  の位置で追加補償を行う.補償により追加された零点  $Z_{ESR}$  及び,極  $P_{\rm fr}$  は次式で現される.

$$Z_{ff} = \frac{1}{2\pi R_1 C_{ff}} \tag{5}$$

図5 極と零点の位置の概略図(補償後)

$$P_{ff} = \frac{1}{2\pi (R_1//R_2)C_{ff}} \tag{6}$$

$$Z_{ESR} = \frac{1}{2\pi R_{ESR} C_O} \tag{7}$$

出力コンデンサの ESR に関しては安定性を考慮する と最大値、最小値が存在する. すなわち図5において、 Z<sub>ESR</sub> はゲインが 0dB となるクロスオーバー周波数と Z<sub>ff</sub> 間に位置して、Pfの位相遅れを打ち消さなければ不安 定となる. ESR が大きい場合は,  $Z_{ESR}$  が低周波に現れる. この結果クロスオーバー周波数が高域へ移動し, 高周波 に複数存在する極の影響で位相が急激に変化し位相余裕 が無くなる. ESR が低すぎる場合は  $Z_{ESR}$  が  $P_{ff}$  から離れ て高周波に現れる.クロスオーバー周波数と比べて Zesa が大きく高域にずれると、零点は補償としての効果をな さず不安定となる. 以上のことから出力コンデンサの選 択は慎重に行う必要がある. 従来の LDO は出力コンデ ンサにタンタルコンデンサなど比較的 ESR が大きな場 合を想定していたが、小容量かつ低 ESR のセラミック コンデンサを用いるためには対策が必要となる.一つ目 の工夫はLDOのDCゲインを下げる方法である. これ により ESR 補償によらず LDO を安定して用いることが できるが、応答性が犠牲となる. もう一つの方法は Pop が高域で生じるオペアンプを用いる方法である. これに よりクロスオーバー周波数を広域にずらすことができ, セラミックコンデンサを用いた場合の零点が安定性改善

に寄与できる.

ただし、セラミックコンデンサは小型であるものの温度特性や DC バイアス特性がタンタルコンデンサと比べて悪く、容量値も数十%変化する.このため十分に位相余裕を確保する設計が必要である.

負荷電流に関しては許容電力面において最大値が存在する. 一方,最小値については負荷  $R_L$  の増加に伴い極  $P_{LOAD}$  がより低域に生じるため,位相余裕が減少する. この結果,軽負荷時の安定性が低下するので,この点も 考慮しなければならない.

#### 4. 設計手順

補償の設計手順としては、まず式 (1)~(4) で求められる各極の位置を把握する.次に低周波にある極を打ち消すように微分補償の零点  $Z_{\rm ff}$  を配置する.続いて微分補償の極  $P_{\rm ff}$  を打ち消すように ESR 補償の零点  $Z_{\rm ESR}$  を配置する. ESR 補償は微分補償の零点  $Z_{\rm ff}$  とクロスオーバー周波数の間になるように配置することで、より位相余裕を確保することができる.以上の設計手順で LDO を安定化する.

#### 5. シミュレーション結果

図 1 において出力電圧  $V_o$ =5V,  $Q_1$ : 2SA562,  $Q_2$ : 2SC1815,  $U_1$ : AD817 を用いた LDO を例に安定性を考える. この回路の極を,式(1)~(4) を用いて理論的に求めると, $P_{OP}$ : 30Hz, $P_{LOAD}$ : 120Hz, $P_{NPN}$ : 300kHz, $P_{PNP}$ : 30MHz に存在する.

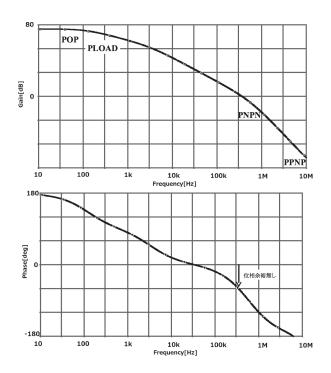

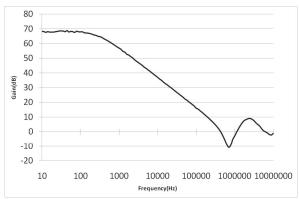

この回路では出力コンデンサにセラミックコンデンサ を用いた場合でも安定することを目的とする. 図1の回 路について回路シミュレーションで求めたボード線図を 図6に示す. 図6からクロスオーバー周波数において位 相余裕がマイナスであることが分かる. この回路に微分 補償,及びESR補償を加えたボード線図を図7に示す. 微分補償の Z<sub>ff</sub> は低域の極を打ち消すために可能な限り 低域に設置している. Z<sub>ff</sub>を低域にするためには式(5)よ り  $C_{\rm ff}$  を大きい値にする必要がある.  $C_{\rm ff}$  は数十 pF が上 限であるため,今回は50pFとした. ESR 補償はセラミッ クコンデンサを用いた場合を想定しており, ESR は 0.05 Ωとしている. 各補償による零点, 極は上記の値から  $Z_{\mathrm{ff}}$ : 28kHz,  $P_{\mathrm{ff}}$ : 62kHz,  $Z_{\mathrm{ESR}}$ : 670kHz で生じる. その 結果、図7ではゲインが0dBの時に位相余裕が30°以 上あることが分かる. このことから, 原理上は補償を加 えることで回路が安定することが分かる.

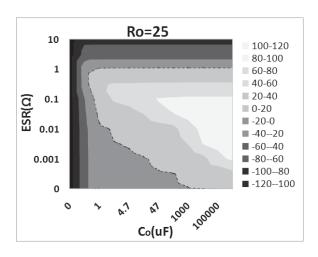

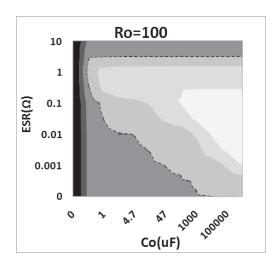

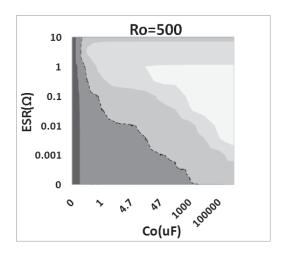

安定性は出力コンデンサ $C_0$ , ESR, 負荷抵抗 $R_L$ の値に大きく影響を受ける。そこで $R_L$ をパラメータとして位相余裕をESR,  $C_0$ の関数として求めた結果を図8に示す。色が白いほど位相余裕が大きく,濃いほど位相余裕が無く悪化していることを示しており,破線が安定限界である。ESR の値が大きい時に不安定となるのは図

図6 シミュレーション回路によるボード線図

図7 シミュレーション回路によるボード線図(補償後)

5において  $Z_{ESR}$  が低周波に来てしまう事が原因である. この結果クロスオーバー周波数が高周波化し、高周波にある複数の極による位相遅れで不安定となる.  $C_0$ ,  $R_L$  の値が小さい程不安定となるのは、図 5 において  $P_{LOAD}$  と  $Z_{ESR}$  が高域に移動し位相余裕がなくなることが原因である. このことからセラミックコンデンサ等の ESR が小さなコンデンサを用いる際には容量を十分に確保す

(a) $R_o$ =25[ $\Omega$ ]の場合

(b) R<sub>0</sub>=100[Ω]の場合

(c) R<sub>o</sub>=500[Ω]の場合

図8 ESR, Co と位相余裕の関係

る,あるいは軽負荷とならないようにするなどの工夫が必要となる.具体的な容量としては数  $\mu F$  程度が妥当である. $0.1 \mu F$  などの値ではセラミックコンデンサの ESR では不安定になる可能性がある.一方,LDO の DC ゲインを低く設計すれば ESR 補償によらず安定とすることが可能であり,コンデンサ容量制限を大きく緩和することができる.この結果,DC ゲインを下げる前の LDO と比べて,小容量かつ低 ESR のコンデンサを用いることができる.一方,DC ゲインの低下により定常偏差と応答性が犠牲となる点には注意しなければならない.ただし,ESR が小さなセラミックコンデンサを用いれば,ステップ変化に対して大きな改善効果が期待できる.

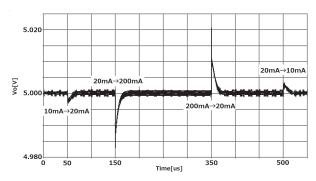

図 9 は負荷電流をステップ変化させた際の出力電圧の応答波形の一例である。今回は  $C_0$ =4.7 $\mu$ F,  $R_{ESR}$ = 0.5  $\Omega$ ,負荷電流の最大値を 200mA,最小値を 10mA とし,10mA  $\rightarrow$  20mA  $\rightarrow$

一方、 $C_0$ =1 $\mu$ F、 $R_{ESR}$ = 0.05  $\Omega$  と小容量、低 ESR とした場合では位相余裕は 20°であった。この場合 DC ゲインを 60dB 程度下げれば先の  $C_0$ =4.7 $\mu$ F、 $R_{ESR}$ = 0.5  $\Omega$ の場合と同レベルの位相余裕となるが、DC ゲインの低下が著しいため問題である。これに対して、DC ゲインの低下を 10dB に抑えれば、40°の位相余裕を確保できるため、設計としては十分と考えられる。

### 6. 実験結果

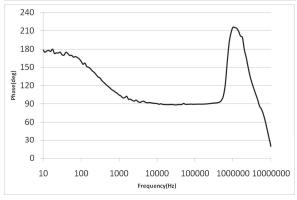

図10は図4の実験回路においてボード線図を測定したものである.

この図とシミュレーション波形を比べると、回路上に含まれる配線インダクタンスやコンデンサの温度特性による容量変化の誤差が考えられるものの、特性全体の概形は一致しており、今回の解析及び位相補償の設計手順の妥当性が示されたといえる.

図9 負荷変動における電圧波形

図10 実験回路によるボード線図

## 5. まとめ

LDO の安定性について詳細な解析を行い、安定性を改善する補償方法とその結果得られる安定領域を明らかにした. LDO において必ず存在するオペアンプ、負荷、トランジスタによる極の位置を把握した上で、微分補償や ESR 補償による零点の位置を設定し、位相余裕を十分に確保する補償を行うことで LDO を安定化させることができる. 特に負荷コンデンサの選定は安定性に大きな影響を与える. 安定性がより求められる場面では容量値が大きく変化しないタンタルコンデンサを用いることが一般手法である. 一方、より省スペース化したい場合は小容量セラミックコンデンサを用いることが適切であり、DC ゲインの再設定も考慮したパラメータ調整で安定化することが可能である.

## 参考文献

- [1] 小浜 輝彦, 野又 佳祐, "LDO レギュレータの安定性について", 福岡大学工学集報 No.87,pp.9-15, 2011年9月

- [2] 古賀健史,小浜輝彦,"LDO レギュレータの安定性 改善について",電気学会産業応用部門大会 Y-37, 2011 年 9 月

- [3] National Semiconductor Application Note 1148, Chester Simpson, 2000 年 5 月

- [4] National Semiconductor Application Note 1482, Chester Simpson, 2006 年 5 月

- [5] 棚木義則,"電子回路シミュレータ PSpice 入門編",CQ 出版社

- [6] 森下勇, "電子回路シミュレータ PSpice リファレンス・ブック", CQ 出版社

- [7] 遠坂俊昭, "電子回路シミュレータ SPICE 実践編", CQ 出版社